### **Features**

- CMOS High Voltage Process: 9V-30V Display Panel Supply Compatible

- 240 Output Channels, Cascadable

- Token-Based Bidirectional Data Transfer: Direct User Control of Scan Rate

- Current Source Magnitude User Control: 4 µA to 1 mA

- 6-Bit Monochromatic/Color Gray-Scale User Control

- Current matching accuracy: ± 2% ± 1.5 µA intra-die ± 1% inter-die

- Monochromatic/Color Voltage Precharge Options

- Built-In A-to-D Converter Monitoring of Display Panel Characteristics

- 3.3 V to 5 V logic supply

- Up to 35 MHz clock frequency

- Gold-Bumped Die @ 60 micron Output Pitch

- TCP packaging

- Companion to Clare Micronix MXED202

128-Channel OLED Row Driver

### Description

The MXED102 is Clare's second-generation OLED column driver offering, which supports up to 240-monochromatic or 80-color OLED pixels. The MXED102's exceptionally tight current-matching of adjacent and cascaded outputs, precharge options, and OLED monitoring capability, ensures uniform luminance and highquality greyscaling in both monochromatic and RGB mode. This is the first ASSP production driver for OLED module OEM's building a new standard in flat-panel displays.

### For All Passive-Matrix Organic-Light-Emitting-Diode Displays

- Monochrome and Color

- Small-Molecule and Polymer

- Current-Sourcing Anode Drivers

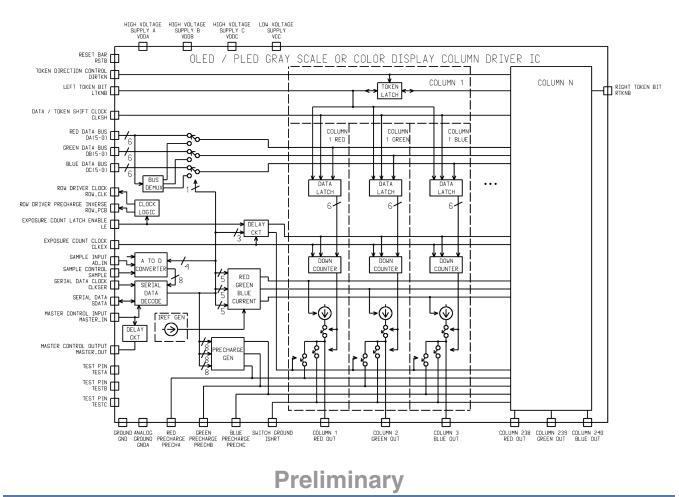

# **Column Driver Block Diagram**

### PRELIMINARY ELECTRICAL DATA SHEET

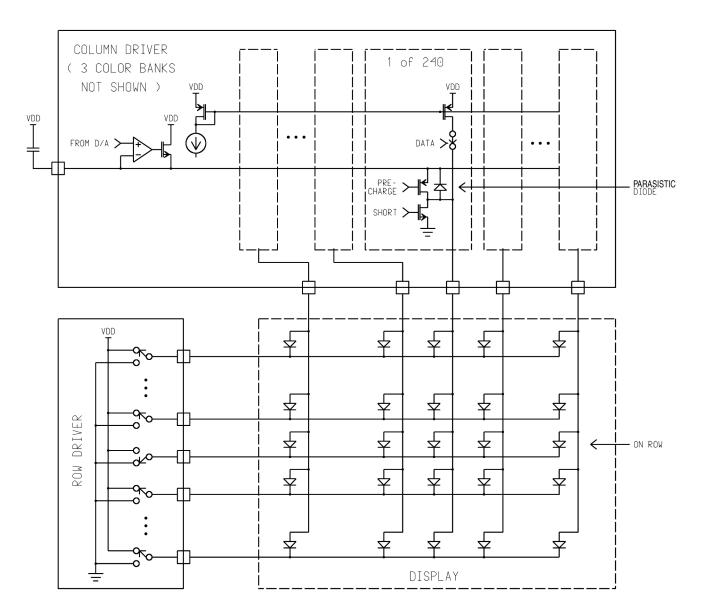

This document is a specification for a digital data driver for Passive Matrix Organic Light Emitting Diode (OLED) and Polymer Light Emitting displays (PLED, PolyLED, LEP, ..., etc) with anodes connected to the columns. The output stage of each channel has a resistive switch to an on chip generated voltage used during precharge and a current source used during data output to minimize non-uniformity caused by spatial and temporal variations of the LED characteristics and by line resistances. The data driver chip is manufactured in a high voltage (30 V) CMOS process and provided in bumped die and TCP (Tape Carrier Package) form.

#### **Description of Operation:**

<u>Overview</u>: The MXED102 is configured via a serial port, and pixel data is updated on a per-row basis via a parallel data bus.

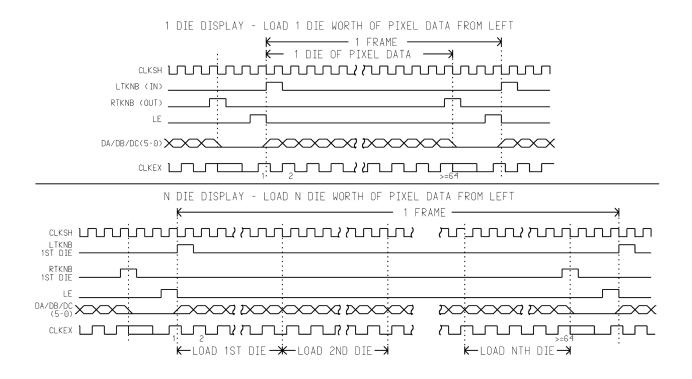

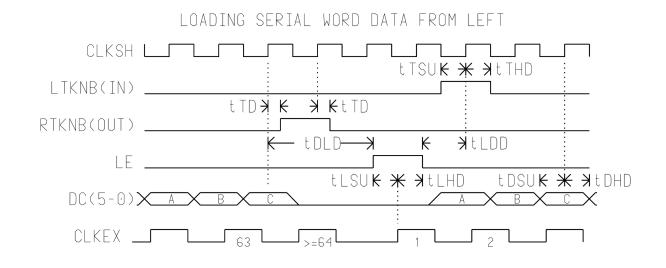

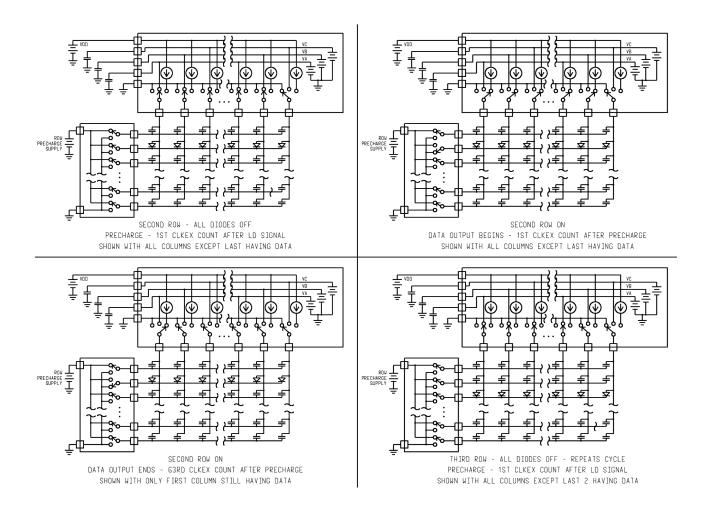

Dynamic Pixel Control: Gray-Scale Control data is loaded into the 6-bit Column Exposure Counters each row scan time, while the previously loaded data is being output to the OLED Display Panel. The control data sets the exposure time from 0 to 63 Exposure Clock times. Successive counters are accessed upon coincidence with the token bit, which is shifted the length of the MXED102 by the Token Shift Clock. In 6-bit Data Mode, Databus C {DC(5-0)} is used to enter per-pixel data, and the Token traverses length of the Chip in 240 Token Shift Clocks. In 18-bit Data Mode, Databusses A, B, and C are used to load three successive pixels in parallel, and the Token traverses length of the Chip in 80 Token Shift Clocks.

<u>Chip Configuration</u>: A display controller may use the serial bus to set the characteristics of all column driver ICs by writing to all column driver ICs in parallel. During write, the controller writes the entire data packet. The controller can also interrogate a single column driver IC, whose MASTER pin is pulled high. Only one column driver IC on a given bus can be designated as master. During read, the controller writes the preamble, start of frame delimiter, register address, and turn around bits. It then tri-states for the bus tri-state and data bits and reads the data.

<u>Color/Monochrome</u>: The MXED102 supports three-each interleaved column Current Magnitude settings and three Precharge Voltages, A,B and C, which may be mapped to R,G,B. Monochrome mode is selected by setting the Color control bit to zero, in which case the Current Magnitude and Precharge Voltage is common.

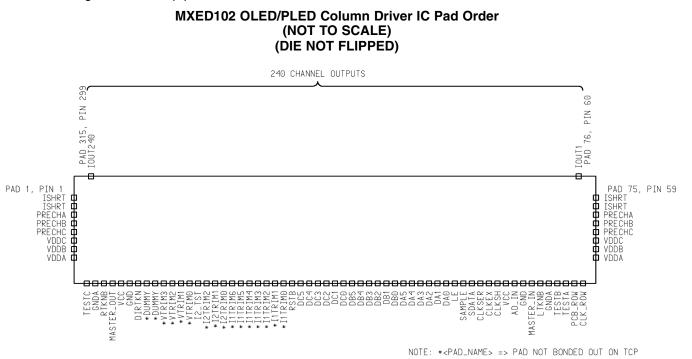

### Package and Pin Out

Below is a diagram of the chip pinout:

# Pin List

| Name              | I/O/A | Description                                                                                                                                                                                                                                                                                                                                                                 |

|-------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDDA,             |       | High voltage supply A/B/C:                                                                                                                                                                                                                                                                                                                                                  |

| VDDB,             | -     |                                                                                                                                                                                                                                                                                                                                                                             |

| VDDC              |       |                                                                                                                                                                                                                                                                                                                                                                             |

| VCC               | -     | Logic supply:                                                                                                                                                                                                                                                                                                                                                               |

| GND               | -     | Ground:                                                                                                                                                                                                                                                                                                                                                                     |

| GNDA              | -     | Analog ground:                                                                                                                                                                                                                                                                                                                                                              |

| ISHRT             | -     | Ground used to short output channels: There can be high currents on this line. It should be separated from the circuit ground pads (GND) to prevent ground bounce.                                                                                                                                                                                                          |

| PRECHA,           | O/A   | Precharge A/B/C: Column precharge voltage outputs. PRECHA/B/C should be tied                                                                                                                                                                                                                                                                                                |

| PRECHB,<br>PRECHC |       | to PRECHA/B/C of all other column drivers to ensure a uniform display precharge<br>and should be bypassed to ground with a capacitor at least 50 times the display<br>capacitance.                                                                                                                                                                                          |

| MASTER_IN         |       | Master In: High input implies chip is master. This input is pulled low internally.                                                                                                                                                                                                                                                                                          |

| MASTER_OUT        | 0     | Master Out: MASTER_IN delayed by 1 LE clock cycle, sampled on rising edge of LE.                                                                                                                                                                                                                                                                                            |

| RSTB              | I     | Reset Bar: Input signal used to reset digital logic for test purposes. This input is pulled high internally.                                                                                                                                                                                                                                                                |

| CLKSH             | I     | Token Shift Clock: Input signal used to shift tokens down the length of the driver IC and latch data into the corresponding columns. The direction of token shift is deter mined by DIRTKN pin.                                                                                                                                                                             |

| LTKNB             | I/O   | Left Token Bit: Input for shift right, output for shift left. Signal is used to pass the tokens into and out of the driver IC. High state represents the presence of token.                                                                                                                                                                                                 |

| RTKNB             | I/O   | Right Token Bit: Input for shift left, output for shift right. Signal is used to pass the tokens into and out of the driver IC. High state represents the presence of token.                                                                                                                                                                                                |

| DIRTKN            | I     | Token Direction Input: Input signal which, when high, causes the token to shift left to right in the driver IC. A low signal causes the token to shift right to left. In the paral lel data mode the token passes through the chip in 80 CLKSH clocks, in the serial data mode the token passes through the chip in 240 CLKSH clocks. This input is pulled high internally. |

| LE                | I     | Latch Enable: Input signal used to begin data output. When data output begins, new data input for the following row can begin.                                                                                                                                                                                                                                              |

| DA(5-0),          | I     | Data A/B/C: Signal buses used to input the exposure data.                                                                                                                                                                                                                                                                                                                   |

| DB(5-0),          |       |                                                                                                                                                                                                                                                                                                                                                                             |

| DC(5-0)           |       |                                                                                                                                                                                                                                                                                                                                                                             |

| CLKEX             | I     | Exposure Clock: Input signal used to clock the driver IC's exposure counter from 0 to 63 for a row exposure. The signal must be cycled at least 64 times between LE pulses to completely cycle the counter. Cycles of CLKEX beyond 64 will have no effect.                                                                                                                  |

| CLKSER            | Ι     | Serial Clock: Clock to write serial data into all column drivers or read serial data from the master column driver.                                                                                                                                                                                                                                                         |

| SDATA             | I/O   | Serial Data: Serial data written to all column drivers or read from the master column driver.                                                                                                                                                                                                                                                                               |

| SAMPLE            | I     | Initiate A/D sample. This input is pulled low internally.                                                                                                                                                                                                                                                                                                                   |

### Pin List (continued)

| AD_IN                     | A | A to D Input: The part can do an A to D conversion on the voltage on this input.                                                                                                                              |

|---------------------------|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TESTA,<br>TESTB,<br>TESTC | A | Test Outputs: The A, B, and C driver bank outputs are muxed to the TESTA, TESTB,<br>and TESTC pads respectively when these pads are pulled low. During normal<br>operation they are left open or tied to VDD. |

| I1TRIM<br>(6:0)           | A | Current Source 1 Trim: These pins must be left open.                                                                                                                                                          |

| I2TRIM<br>(3:0)           | А | Current Source 2 Trim: These pins must be left open.                                                                                                                                                          |

| VTRIM<br>(3:0)            | А | Voltage Source Trim: These pins must be left open.                                                                                                                                                            |

| I2_TST                    | А | Current Source 2 Monitor: This pin must be left open.                                                                                                                                                         |

| IOUT(240-1)               | А | Channel Outputs: The outputs of the driver IC that directly drives the display panel                                                                                                                          |

| CLK_ROW                   | 0 | Row Clock: Signal intended to drive the row driver IC shift data clock                                                                                                                                        |

| PCB_ROW                   | 0 | Row Precharge: Signal intended to drive the row driver IC precharge input                                                                                                                                     |

| Noto: A -> ana            |   | ligital input 0 -> digital output                                                                                                                                                                             |

Note: A => analog, I => digital input, O => digital output

# **ELECTRICAL SPECIFICATIONS**

Positive currents flow into the part, negative currents flow out of the part, largest currents are currents with the greatest absolute magnitude.

### Absolute Maximum Ratings:

| Parameter           | Operating Condition | Min  | Тур | Max  | Units |

|---------------------|---------------------|------|-----|------|-------|

| Ambient temp        | -                   | -65  | -   | 155  | ۵°C   |

| Low voltage supply  | -                   | -0.3 | -   | 7.0  | V     |

| High voltage supply | -                   | -0.3 | -   | 35.0 | V     |

### **Operating Conditions:**

Unless otherwise stated, all parameters are specified for the following operating conditions.

| Parameter             | Sym                 | Operating<br>Condition | Min | Тур | Max | Units |

|-----------------------|---------------------|------------------------|-----|-----|-----|-------|

| Ambient temp          | TA                  | -                      | 0   | -   | 70  | °C    |

| Low voltage supply    | VCC                 | -                      | 3.0 | -   | 5.5 | V     |

| High voltage supplies | VDDA,<br>VDDB, VDDC | -                      | 9.0 | -   | 30  | V     |

# Supply Currents:

4

| Parameter                                                   | Sym           | Operating<br>Condition                                                                         | Min | Тур | Max               | Units |

|-------------------------------------------------------------|---------------|------------------------------------------------------------------------------------------------|-----|-----|-------------------|-------|

| High voltage supply<br>current during standby               | IDD<br>(stby) | -                                                                                              | -   | -   | TBD               | uA    |

| Internal high voltage<br>supply current during<br>operation | IDD<br>(int)  | Current from VDD not<br>flowing out outputs or<br>into precharge circuit<br>lout = per channel | -   | -   | 14 mA+<br>12xlout | mA    |

| Low voltage supply<br>current during standby                | ICC<br>(stby) | -                                                                                              | -   | -   | TBD               | uA    |

| Low voltage supply current during operation                 | ICC           | -                                                                                              | -   | -   | 10                | mA    |

# **Digital Inputs:**

| Parameter          | Sym | Operating Condition | Min     | Тур | Max | Units |

|--------------------|-----|---------------------|---------|-----|-----|-------|

| Input low voltage  | VIL | -                   | -       | -   | 0.5 | V     |

| Input high voltage | VIH | -                   | VCC-0.5 | -   | -   | V     |

| Input current      | П   | -                   | -10     | -   | 10  | uA    |

# **Digital Outputs:**

| Parameter             | Sym | Operating Condition    | Min     | Тур | Max | Units |

|-----------------------|-----|------------------------|---------|-----|-----|-------|

| Output low voltage    | VOL | lout = 100 uA          | -       | -   | 0.4 | V     |

| Output high voltage   | VOH | lout = -100 uA         | VCC-0.4 | -   | -   | V     |

| Output rise/fall time | TRF | 10 to 90 %, Cload=5 pF | -       | -   | 2.0 | nS    |

# **Serial Configuration Bus:**

### **Bus Operation:**

The controller uses the serial bus to set the characteristics of all column driver ICs by writing to all column driver ICs in parallel. During write, the controller writes the entire data packet. The controller can also inter rogate a single column driver IC, who's MASTER pin is pulled high. Only 1 column driver IC on a given bus can be designated as master. During read, the controller writes the preamble, start of frame delimiter, reg ister address, and turn around bits. It then tri-states for the bus tri-state and data bits and reads the data.

### **Data Packet:**

The data packet consists of:

- 14 bit preamble of all 1's

- 2 bit start of frame delimiter (SFD)

- 6 bit register address MSB first

- 1 turn around bit (TA)

- 1 bus tristate (BT)

- 8 bit data packet MSB first

Write => write data to all column driver ICs

Read => read data from master column driver IC

Data order => Preamble first, data last; MSB first, LSB last

| R/W   | Preamble          | SFD | Reg Address | TA | BT | Data      |

|-------|-------------------|-----|-------------|----|----|-----------|

| write | 1111 1111 1111 11 | 00  | ΑΑΑΑ ΑΑ     | 0  | 0  | DDDD DDDD |

| read  | 1111 1111 1111 11 | 01  | ΑΑΑΑ ΑΑ     | 0  | Z  | DDDD DDDD |

### **Input Registers**

# Register Address 0 - Test Register

Eight bits of data can be written to and read from this register in order to test the serial port. This register has no effect on the column driver.

**Register Address 1 - Control Register 1**

| Bit(s) | Name                     | Description                                                                                                                                                                                                                     | Default |

|--------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 7      | Freeze Master            | Modes:<br>1 => MASTER_OUT pin is not changed<br>0 => Normal, MASTER_OUT is updated to<br>MASTER_IN on rising edge of LE                                                                                                         | 0       |

| 6      | Disable Precharge Driver | Modes:<br>1 => Precharge circuit is disabled<br>0 => Normal                                                                                                                                                                     | 0       |

| 5      | Standby                  | Modes:<br>1 => Part is operating normally<br>0 => Part is in low power standby mode                                                                                                                                             | 0       |

| 4      | Short Channels           | Modes:<br>1 => Channels are all shorted to ground after the<br>CLKEX count reaches 64<br>0 => Each channel is individually shorted to ground<br>after its current source is tristated                                           | 0       |

| 3      | Color Mode               | Modes:<br>0 => Monochrome mode<br>1 => Color mode                                                                                                                                                                               | 0       |

| 2      | Data Mux                 | Modes:<br>0 => DA(5-0), DB(5-0), DC(5-0) data words are read<br>serially from the DC(5-0) pins. The DA(5-0) and<br>DB(5-0) pins are unused.<br>1 => DA(5-0), DB(5-0), DC(5-0) pins used to read<br>their respective data words. | 0       |

| 1-0    | Test Mode(1:0)           | Modes:<br>00 => Normal operation<br>01 => Test mode 1<br>10 => Test mode 2<br>11 => Test mode 3                                                                                                                                 | 00      |

#### **Register Address 2 - Control Register 2**

| Bit(s) | Name            | Description           | Default |

|--------|-----------------|-----------------------|---------|

| 7-2    | Undefined       | -                     | -       |

| 1      | Fast Conversion | Modes:                | -       |

| -      | -               | 0 => Normal operation | 0       |

| -      | -               | 1 =>                  | -       |

| 0      | High A/D Gain   | Modes:                | -       |

| -      | -               | 0 => Normal operation | 0       |

Register Address 3 - A Output Group Data Current Magnitude Register

The 5 LSB bits determine the magnitude of A output group current during data output.

Register Address 4 - B Output Group Data Current Magnitude Register

The 5 LSB bits determine the magnitude of B output group current during data output.

Register Address 5 - C Output Group Data Current Magnitude Register

The 5 LSB bits determine the magnitude of C output group current during data output.

Register Address 6 - A Output Group Precharge Voltage Magnitude Register

The 8 bits determine the magnitude of A output group voltage during precharge.

Register Address 7 - B Output Group Precharge Voltage Magnitude Register

The 8 bits determine the magnitude of B output group voltage during precharge.

Register Address 8 - C Output Group Precharge Voltage Magnitude Register

The 8 bits determine the magnitude of C output group voltage during precharge.

Register Address 8 - C Output Group Precharge Voltage Magnitude Register

The 8 bits determine the magnitude of C output group voltage during precharge.

Register Address 9 - Precharge Count Register

The 3 LSB bits set the precharge time to 0 to 7 CLKEX clock counts.

Register Address 10- A/D Converter Control Register

This register determines which signal is monitored by the A/D converter.

| Bit(s) | Name        | Description                              | Default |

|--------|-------------|------------------------------------------|---------|

| 7-4    | UNDEFINED   | -                                        | -       |

| 3-0    | ad_sel(3:0) | 0xF => Measure VDDA ( Low Gain )         | 0000    |

|        |             | 0xE => Measure TESTA ( Low Gain )        |         |

|        |             | 0xD => Measure IOUT231 ( Low Gain )      |         |

|        |             | 0xC => Measure IOUT6 ( Low Gain )        |         |

|        |             | 0xB=> Measure VDDB ( Low Gain )          |         |

|        |             | 0xA => Measure TESTB ( Low Gain )        |         |

|        |             | 0x9 => Measure IOUT232 ( Low Gain )      |         |

|        |             | 0x8 => Measure IOUT7 ( Low Gain )        |         |

|        |             | 0x7 => Measure VDDC ( Low Gain )         |         |

|        |             | 0x6 => Measure TESTC ( Low Gain )        |         |

|        |             | 0x5 => Measure IOUT233 ( Low Gain )      |         |

|        |             | 0x4 => Measure IOUT8 ( Low Gain )        |         |

|        |             | 0x3 - 0x2 => Undefined                   |         |

|        |             | 0x1 => Measure AD_IN input ( High Gain ) |         |

|        |             | 0x0 => Input grounded                    |         |

## Registers 11 thru 63 - Undefined

### **Output Registers**

### Register Address 0 - Test Register

# **Register Address 1 - Status Register 0**

| Bit(s) | Name      | Description | Default |

|--------|-----------|-------------|---------|

| 7-0    | Undefined | -           | -       |

### Register Address 2 - A/D Converter Output Register

### Registers 3 thru 63 - Undefined

#### Power on Reset:

The part contains a power on reset circuit that ensures that the serial bus data registers come up in their default value when VCC is cycled on. This brings up the part in its standby mode.

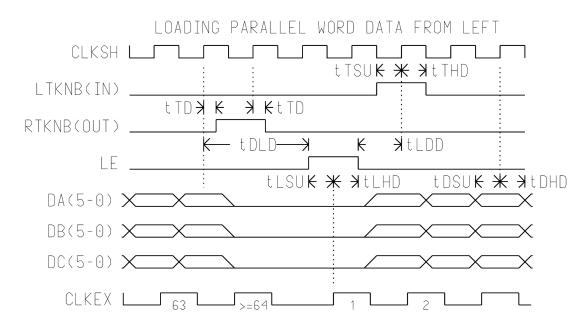

### Digital Timing:

| Parameter                                      | Sym                                                                          | Operating Conditions       | Min | Тур | Max | Unit |

|------------------------------------------------|------------------------------------------------------------------------------|----------------------------|-----|-----|-----|------|

| Shift clock frequency                          | -                                                                            | -                          | -   | -   | 25  | MHz  |

| Shift clock minimum high<br>or low pulse width | -                                                                            | -                          | 16  | -   | -   | nS   |

| Exposure clock frequency                       | -                                                                            | Control reg 2, bit $1 = 0$ | 1.0 | -   | 10  | MHz  |

|                                                |                                                                              | Control reg 2, bit 1 = 1   | -   | -   | 1.0 | MHz  |

| Exposure clock minimum high or low pulse width | -                                                                            | -                          | 80  | -   | -   | nS   |

| Data and token setup/hold time                 | t <sub>DSU</sub> , t <sub>TSU</sub> ,<br>t <sub>DHD</sub> , t <sub>THD</sub> | -                          | 10  | -   | -   | nS   |

| Latch enable setup/hold time                   | t <sub>LSU</sub> , t <sub>LHD</sub>                                          | -                          | 40  | -   | -   | nS   |

| Token bit output delay                         | t <sub>TD</sub>                                                              | -                          | -   | -   | 15  | nS   |

| Last data to latch enable time                 | t <sub>DLD</sub>                                                             | -                          | 200 | -   | -   | nS   |

| Latch disable to new data time                 | t <sub>LDD</sub>                                                             | -                          | 10  | -   | -   | nS   |

#### Precharge Voltage Generator:

| Parameter                   | Sym              | Operating Condition                | Min | Тур | Max | Unit |

|-----------------------------|------------------|------------------------------------|-----|-----|-----|------|

| Precharge voltage generator | V <sub>PRE</sub> | V <sub>PBF</sub> = 30 * N / 256    |     |     |     |      |

| voltage and voltage error   |                  | for N = reg value,                 |     |     |     |      |

|                             |                  | 0 < N < 256                        | - 2 | 0   | + 2 | %    |

|                             |                  | 4 < V <sub>PRE</sub> < VDD-4       |     |     |     |      |

|                             |                  | -30 mA < I <sub>PRE</sub> < -50 mA |     |     |     |      |

|                             |                  | 4 < V <sub>PRE</sub> < VDD-3       |     |     |     |      |

|                             |                  | -5 mA < I <sub>PRE</sub> < -30 mA  |     |     |     |      |

| Precharge voltage generator | -                | 5 < V <sub>PBF</sub> < VDD-4,      | -   | -   | TBD | ohms |

| output impedance            |                  | I = -15 mA                         |     |     |     |      |

| Load capacitance            | -                | -                                  | -   | -   | 5   | uF   |

# Output Current Channels:

| Parameter                                           | Sym              | Operating Condition                 | Min  | Тур | Max  | Unit |

|-----------------------------------------------------|------------------|-------------------------------------|------|-----|------|------|

| Channel output impedance                            | -                | 5 < V <sub>PRE</sub> < VDD-4,       | -    | -   | 2000 | ohms |

| during precharge                                    |                  | $V_{PRE} - V_{IOUT} < 4 V$          |      |     |      |      |

| Channel output charging                             | -                | 5 < V <sub>PBE</sub> < VDD-4,       | -2.3 | -   | -    | mA   |

| current during precharge                            |                  | $V_{PRE} - V_{IOUT} > 4 V$          |      |     |      |      |

| Driver output current source                        | I <sub>OUT</sub> | I <sub>OUT</sub> = -4 uA x 1.2 ** N |      |     |      |      |

| current and current error                           |                  | for $N = reg$ value,                | -    | -   | -    | -    |

|                                                     |                  | 0 <u>≤</u> N < 32,                  |      |     |      |      |

|                                                     |                  | 0 < V <sub>IOUT</sub> < VDD-3       |      |     |      |      |

|                                                     |                  | -20 uA < I <sub>IOUT</sub> < -75 uA | -3   | -   | +3   | uA   |

|                                                     |                  | -75 uA < I <sub>IOUT</sub> < -1 mA  | -4   | -   | +4   | %    |

| Single die, per bank driver                         |                  | 0 < V <sub>IOUT</sub> < VDD-3,      | -    | -   | -    | -    |

| output current source matching                      | -                | V <sub>IOUT</sub> mismatch < 2 V    |      |     |      |      |

|                                                     |                  | -20 uA < I <sub>IOUT</sub> < -75 uA | -1.5 | -   | +1.5 | uA   |

|                                                     |                  | -75 uA < I <sub>IOUT</sub> < -1 mA  | -2   | -   | +2   | %    |

| Die to die, per bank average                        |                  | 0 < V <sub>IOUT</sub> < VDD-3,      | -    | -   | -    | -    |

| driver output current source                        | -                | V <sub>OUT</sub> mismatch < 2 V     |      |     |      |      |

| matching                                            |                  | 20 uA < I <sub>IOUT</sub> < 150 uA  | -1.5 | -   | 1.5  | uA   |

|                                                     |                  | -150 uA < I <sub>IOUT</sub> < -1 mA | -1   | -   | 1    | %    |

| Exposure clock rising edge to output going high/low | -                | Delay to 50% point                  | -    | -   | 220  | nS   |

| Channel output current rise/fall time               | -                | 10% to 90%                          | -    | -   | 250  | nS   |

| Shorting switch on resistance to ISHRT pin          | -                | V <sub>IOUT</sub> < 8 V             | -    | -   | 400  | ohms |

| Shorting switch discharge current to ISHRT pin      | -                | V <sub>IOUT</sub> > 8 V             | 25   | -   | -    | mA   |

# Chip Monitor Analog to Digital Converter:

The ADC is intended to be used to calibrate the precharge circuit. The ADC on the column driver chip designated as the master can be monitored by the controller. Which parameter the ADC is monitoring is determined by the A/D Converter Control Register. Results can be monitored on the A/D Converter Output Register.

| Parameter                       | Sym | Operating Condition        | Min     | Тур | Max    | Unit   |

|---------------------------------|-----|----------------------------|---------|-----|--------|--------|

| Bits                            | -   | -                          | -       | 8   | -      | -      |

| Linearity                       | -   | -                          | 5 LSB   | -   | .5 LSB | -      |

| Accuracy                        | -   | -                          | - 1 LSB | -   | 1 LSB  | -      |

| Output for low voltage input    | -   | Vout(8 bit word) =         | -       | -   | -      | -      |

|                                 |     | 255 * Vin / 5.0            |         |     |        |        |

| Output for high voltage input   | -   | Vout(8 bit word) =         | -       | -   | -      | -      |

|                                 |     | 255 * Vin / 30.0           |         |     |        |        |

| Conversion time in CLKEX counts | -   | Control reg 2, bit $1 = 0$ | 896     | -   | -      | CLKEX  |

|                                 |     | Control reg 2, bit 1 = 1   | 112     | -   | -      | counts |

Preliminary

# **Timing Diagrams:**

# Load Data Pattern Macro Timing

# Data Output Timing

| LE       | DISCHARGE SET TO N COUNTS, PRECHARGE SET TO 3 COUNTS                         |

|----------|------------------------------------------------------------------------------|

| CLKEX    | ARGE PRECHARGE DATA OUTPUT DISCHARGE - PRECHARGE - DISCHARGE - A DATA OUTPUT |

| PCB_ROW  |                                                                              |

| CLK_ROW  |                                                                              |

| LE       | DISCHARGE SET TO 0 COUNTS, PRECHARGE SET TO 3 CDUNTS                         |

|          | A K CLHU<br>                                                                 |

| PC B_ROW |                                                                              |

| CLK_ROW  |                                                                              |

|          | DISCHARGE SET TO 3 COUNTS, PRECHARGE SET TO 0 COUNTS                         |

| LE       | LLSUA K KILHD                                                                |

| CLKEX    |                                                                              |

| PC B_ROW | DATA OUT ———————————————————————————————————                                 |

| CL.K_ROW |                                                                              |

### **APPLICATION NOTES:**

# Application Note 1 - Parasitic Diode in Precharge Circuit:

The MX823 has a parasitic diode connected between the precharge reference pin PRECHA and column outputs 1, 4, ..., 238, and between PRECHB and outputs 2, 5, ..., 239, and between PRECHC and outputs 3, 6, ..., 240 as shown below. This means that the precharge voltage must be set above the display diode anode voltages during calibration and at or above display diode anode voltages during operation or output current will flow through the parasitic diodes and not the display.

#### **Display Block Diagram**

# Application Note 2 - Display Switching Pattern:

The diagram below shows the switching sequence the row and column drivers go through.

### SEMICONDUCTOR DIE DATA SHEET

The MXED102 is a digital data driver for Passive Matrix Organic Light Emitting Diode (OLED) and Polymer Light Emitting Diode (PLED, PolyLED, LEP, . . . etc.) displays, with anodes connected to the columns. This document specificies the physical and mechanical properties of MXED102 semiconductor die, as provided in wafer form.

#### DIMENSIONS

Die Size

"X Dimension" Center Scribe to Center Scribe

"Y Dimension" Scribe to Center Scribe

**Die Thickness**

Unthinned (Non Back Lapped Wafer) Thickness: 25 mils

### **BONDING PADS**

#### Locations and Sizes - Driver Outputs

|                  |                  |          | I                  | MXED1            | 02 PAD    | LOCATIO            | NS                 |          |                    |                    |          |

|------------------|------------------|----------|--------------------|------------------|-----------|--------------------|--------------------|----------|--------------------|--------------------|----------|

|                  |                  |          | co                 | ORDINATES        | S REFEREN | CE TO CENTER       | OF PAD             |          |                    |                    |          |

| SOUA             | RE(60X BY        | 60Y)     | RE                 | CT(40X BY        | 60Y)      | REC                | T(40X BY 6         | (0Y)     | REC                | CT(40X BY          | 60Y)     |

| NAME             | X                | Y        | NAME               | X                | V Y       | NAME               | X                  | V Y      | NAME               | X                  | V Y      |

| IOUT0            | 338.6            | 30       | IOUT61             | 4249.3           | 30        | IOUT124            | 8214.1             | 30       | IOUT187            | 12179.1            | 30       |

| IOUT1            | 424.9            | 30       | IOUT62             | 4309.3           | 30        | IOUT125            | 8274.1             | 30       | IOUT188            | 12239.1            | 30       |

| IOUT2            | 511.3            | 30       | IOUT63             | 4369.3           | 30        | IOUT126            | 8334.1             | 30       | IOUT189            | 12299.1            | 30       |

|                  | CT(40X BY 6      |          | IOUT64             | 4429.3           | 30        | IOUT127            | 8394.1             | 30       | IOUT190            | 12359.1            | 30       |

| NAME             | X                | Y        | IOUT65             | 4489.3           | 30        | IOUT128            | 8454.1             | 30       | IOUT191            | 12419.1            | 30       |

| IOUT3            | 584.4            | 30       | IOUT66             | 4549.3           | 30        | IOUT129            | 8514.1             | 30       | IOUT192            | 12479.1            | 30       |

| IOUT4            | 644.4            | 30       | IOUT67             | 4609.3           | 30        | IOUT130            | 8574.1             | 30       | IOUT193            | 12539.1            | 30       |

| IOUT5            | 704.4            | 30       | IOUT68             | 4669.3           | 30        | IOUT131            | 8634.1             | 30       | IOUT194            | 12599.1            | 30       |

| IOUT6<br>IOUT7   | 764.4<br>824.4   | 30<br>30 | IOUT69<br>IOUT70   | 4729.3<br>4789.3 | 30<br>30  | IOUT132<br>IOUT133 | 8694.1<br>8754.1   | 30<br>30 | IOUT195            | 12659.1<br>12719.1 | 30<br>30 |

| IOUT7            | 884.4            | 30       | IOUT70             | 4789.3           | 30        | IOUT133            | 8754.1             | 30       | IOUT196            | 12719.1            | 30       |

| IOUT9            | 944.4            | 30       | IOUT72             | 4909.3           | 30        | IOUT134            | 8874.1             | 30       | IOUT197            | 12839.1            | 30       |

| IOUT10           | 1004.4           | 30       | IOUT73             | 4969.3           | 30        | IOUT136            | 8934.1             | 30       | IOUT199            | 12899.1            | 30       |

| IOUT11           | 1064.4           | 30       | IOUT74             | 5029.3           | 30        | IOUT137            | 8994.1             | 30       | IOUT200            | 12959.1            | 30       |

| IOUT12           | 1124.4           | 30       | IOUT75             | 5089.3           | 30        | IOUT138            | 9054.1             | 30       | IOUT201            | 13019.1            | 30       |

| IOUT13           | 1184.4           | 30       | IOUT76             | 5149.3           | 30        | IOUT139            | 9114.1             | 30       | IOUT202            | 13079.1            | 30       |

| IOUT14           | 1244.4           | 30       | IOUT77             | 5209.3           | 30        | IOUT140            | 9174.1             | 30       | IOUT203            | 13139.1            | 30       |

| IOUT15           | 1304.4           | 30       | IOUT78             | 5269.3           | 30        | IOUT141            | 9234.1             | 30       | IOUT204            | 13199.1            | 30       |

| IOUT16           | 1364.4           | 30       | IOUT79             | 5329.3           | 30        | IOUT142            | 9294.1             | 30       | IOUT205            | 13259.1            | 30       |

| IOUT17           | 1424.4           | 30       | IOUT80             | 5389.3           | 30        | IOUT143            | 9354.1             | 30       | IOUT206            | 13319.1            | 30       |

| IOUT18           | 1484.4           | 30       | IOUT81             | 5449.3           | 30        | IOUT144            | 9414.1             | 30       |                    | RE(60X B           |          |

| IOUT19           | 1544.4           | 30       | IOUT82             | 5509.3           | 30        | IOUT145            | 9474.1             | 30       | NAME               | X                  | Y        |

| IOUT20           | 1604.4           | 30       | IOUT83             | 5569.3           | 30        | IOUT146            | 9534.1             | 30       | IOUT207            | 13392              | 30       |

| IOUT21           | 1664.4           | 30<br>30 | IOUT84             | 5629.3           | 30<br>30  |                    | RE(60X BY          |          | IOUT208            | 13478.4            | 30<br>30 |

| IOUT22<br>IOUT23 | 1724.4<br>1784.4 | 30       | IOUT85             | 5689.3<br>5749.3 | 30        | IOUT147            | <b>X</b><br>9607   | Y<br>30  | IOUT209<br>IOUT210 | 13564.7<br>13678.2 | 30       |

| IOUT23           | 1844.4           | 30       |                    | ARE(60X B        |           | IOUT147            | 9693.4             | 30       | IOUT210            | 13764.5            | 30       |

| IOUT25           | 1904.4           | 30       | NAME               |                  | Y         | IOUT140            | 9779.7             | 30       | IOUT212            | 13850.9            | 30       |

| IOUT26           | 1964.4           | 30       | IOUT87             | 5822.2           | 30        | IOUT150            | 9893.4             | 30       |                    | CT(40X BY          |          |

|                  | RE(60X BY        |          | IOUT88             | 5908.6           | 30        | IOUT151            | 9979.7             | 30       | NAME               | X                  | Y        |

| NAME             | X                | Ý        | IOUT89             | 5994.9           | 30        | IOUT152            | 10066.1            | 30       | IOUT213            | 13924              | 30       |

| IOUT27           | 2037.3           | 30       | IOUT90             | 6108.4           | 30        | REC                | T(40X BY 6         | 0Y)      | IOUT214            | 13984              | 30       |

| IOUT28           | 2123.7           | 30       | IOUT91             | 6194.7           | 30        | NAME               | Х                  | Y        | IOUT215            | 14044              | 30       |

| IOUT29           | 2210             | 30       | IOUT92             | 6281.1           | 30        | IOUT153            | 10139.1            | 30       | IOUT216            | 14104              | 30       |

| IOUT30           | 2323.6           | 30       |                    | CT(40X BY        | · · ·     | IOUT154            | 10199.1            | 30       | IOUT217            | 14164              | 30       |

| IOUT31           | 2409.9           | 30       | NAME               | X                | Y         | IOUT155            | 10259.1            | 30       | IOUT218            | 14224              | 30       |

| IOUT32           | 2496.3           | 30       | IOUT93<br>IOUT94   | 6354.1           | 30<br>30  | IOUT156            | 10319.1            | 30<br>30 | IOUT219            | 14284<br>14344     | 30<br>30 |

| NAME             | CT(40X BY 60     | VT)<br>Y | IOUT94             | 6414.1<br>6474.1 | 30        | IOUT157<br>IOUT158 | 10379.1<br>10439.1 | 30       | IOUT220            | 14344              | 30       |

| IOUT33           | 2569.3           | 30       | IOUT96             | 6534.1           | 30        | IOUT158            | 10439.1            | 30       | IOUT222            | 14464              | 30       |

| IOUT34           | 1629.3           | 30       | IOUT97             | 6594.1           | 30        | IOUT160            | 10559.1            | 30       | IOUT223            | 14524              | 30       |

| IOUT35           | 2689.3           | 30       | IOUT98             | 6654.1           | 30        | IOUT161            | 10619.1            | 30       | IOUT224            | 14584              | 30       |

| IOUT36           | 2749.3           | 30       | IOUT99             | 6714.1           | 30        | IOUT162            | 10679.1            | 30       | IOUT225            | 14644              | 30       |

| IOUT37           | 2809.3           | 30       | IOUT100            | 6774.1           | 30        | IOUT163            | 10739.1            | 30       | IOUT226            | 14704              | 30       |

| IOUT38           | 2869.3           | 30       | IOUT101            | 6834.1           | 30        | IOUT164            | 10799.1            | 30       | IOUT227            | 14764              | 30       |

| IOUT39           | 2929.3           | 30       | IOUT102            | 6894.1           | 30        | IOUT165            | 10859.1            | 30       | IOUT228            | 14824              | 30       |

| IOUT40           | 2989.3           | 30       | IOUT103            | 6954.1           | 30        | IOUT166            | 10919.1            | 30       | IOUT229            | 14884              | 30       |

| IOUT41           | 3049.3           | 30       | IOUT104            | 7014.1           | 30        | IOUT167            | 10979.1            | 30       | IOUT230            | 14944              | 30       |

| IOUT42           | 3109.3           | 30       | IOUT105            | 7074.1           | 30        | IOUT168            | 11039.1            | 30       | IOUT231            | 15004              | 30       |

| IOUT43<br>IOUT44 | 3169.3<br>3229.3 | 30       | IOUT106            | 7134.1           | 30        | IOUT169<br>IOUT170 | 11099.1            | 30       | IOUT232<br>IOUT233 | 15064              | 30       |

| IOUT44<br>IOUT45 | 3229.3           | 30<br>30 | IOUT107<br>IOUT108 | 7194.1<br>7254.1 | 30<br>30  | IOUT170            | 11159.1<br>11219.1 | 30<br>30 | IOUT233            | 15124<br>15184     | 30<br>30 |

| IOUT45           | 3289.3           | 30       | IOUT108            | 7254.1           | 30        | IOUT171            | 11279.1            | 30       | IOUT234            | 15184              | 30       |

| IOUT48           | 3409.3           | 30       | IOUT109            | 7374.1           | 30        | IOUT172            | 11339.1            | 30       | IOUT235            | 15304              | 30       |

| IOUT48           | 3469.3           | 30       | IOUT111            | 7434.1           | 30        | IOUT174            | 11399.1            | 30       |                    | ARE(60X B          |          |

| IOUT49           | 3529.3           | 30       | IOUT112            | 7494.1           | 30        | IOUT175            | 11459.1            | 30       | NAME               | X                  | Y        |

| IOUT50           | 3589.3           | 30       | IOUT113            | 7554.1           | 30        | IOUT176            | 11519.1            | 30       | IOUT237            | 15376.9            | 30       |

| IOUT51           | 3649.3           | 30       | IOUT114            | 7614.1           | 30        | IOUT177            | 11579.1            | 30       | IOUT238            | 15463.3            | 30       |

| IOUT52           | 3709.3           | 30       | IOUT115            | 7674.1           | 30        | IOUT178            | 11639.1            | 30       | IOUT239            | 15549.6            | 30       |

| IOUT53           | 3769.3           | 30       | IOUT116            | 7734.1           | 30        | IOUT179            | 11699.1            | 30       |                    |                    |          |

| IOUT54           | 3829.3           | 30       | IOUT117            | 7794.1           | 30        | IOUT180            | 11759.1            | 30       |                    |                    |          |

| IOUT55           | 3889.3           | 30       | IOUT118            | 7854.1           | 30        | IOUT181            | 11819.1            | 30       |                    |                    |          |

| IOUT56           | 3949.3           | 30       | IOUT119            | 7914.1           | 30        | IOUT182            | 11879.1            | 30       | -                  |                    |          |

| IOUT57           | 4009.3           | 30       | IOUT120            | 7974.1           | 30        | IOUT183            | 11939.1            | 30       | 4                  |                    |          |

| IOUT58           | 4069.3           | 30       | IOUT121            | 8034.1           | 30        | IOUT184            | 11999.1            | 30       | {                  |                    |          |

| IOUT59           | 4129.3           | 30       | IOUT122            | 8094.1           | 30        | IOUT185            | 12059.1            | 30       | -                  |                    |          |

| IOUT60           | 4189.3           | 30       | IOUT123            | 8154.1           | 30        | IOUT186            | 12119.1            | 30       | ]                  |                    |          |

The information contained on this page is preliminary. Although the order of the bond pad will remain the same, the XY dimensions in the final document may vary slightly. Please take this possibility into consideration when doing any chip on board layouts.

# Interface I/O

#### MXED102 PAD LOCATIONS

#### COORDINATES REFERENCE LOWER LEFT EDGE

|           |         | SQUA   |

|-----------|---------|--------|

| NAME      | Х       | Y      |

| LK_ROW    | 314.2   | 1853.3 |

| CB_ROW    | 734.2   | 1853.3 |

| TESTA     | 1100.5  | 1853.3 |

| TESTB     | 1392.8  | 1853.3 |

| GNDA      | 1614.2  | 1853.3 |

| LTKNB     | 1942.2  | 1853.3 |

| MASTER_IN | 2226.9  | 1853.3 |

| GNDA      | 2442.7  | 1853.3 |

| AD_IN     | 2720    | 1853.3 |

| VCC       | 2943.9  | 1853.3 |

| CLKSH     | 3070.7  | 1853.3 |

| CLKEX     | 3286.4  | 1853.3 |

| CLKSER    | 3502.1  | 1853.3 |

| SDATA     | 3853.1  | 1853.3 |

| SAMPLE    | 4137.8  | 1853.3 |

| LE        | 4353.5  | 1853.3 |

| DA0       | 4569.2  | 1853.3 |

| DA1       | 4784.9  | 1853.3 |

| DA2       | 5000.6  | 1853.3 |

| DA3       | 7927.8  | 1853.3 |

| DA4       | 8143.5  | 1853.3 |

| DA5       | 8359.2  | 1853.3 |

| DB0       | 8574.9  | 1853.3 |

| DB1       | 8790.6  | 1853.3 |

| DB2       | 9006.3  | 1853.3 |

| DB3       | 9222    | 1853.3 |

| DB4       | 9437.7  | 1853.3 |

| DB5       | 9653.4  | 1853.3 |

| DC0       | 9869.1  | 1853.3 |

| DC1       | 10084.8 | 1853.3 |

| DC2       | 10300.5 | 1853.3 |

| DC3       | 10516.2 | 1853.3 |

| DC4       | 10731.9 | 1853.3 |

| DC5       | 10947.6 | 1853.3 |

| RSTB      | 11163.3 | 1853.3 |

| I1TRIM0   | 11307   | 1853.3 |

| I1TRIM1   | 11447.9 | 1853.3 |

| I1TRIM2   | 11588.8 | 1853.3 |

| I1TRIM3   | 11729.7 | 1853.3 |

| I1TRIM4   | 11870.6 | 1853.3 |

| I1TRIM5   | 12011.5 | 1853.3 |

| I1TRIM6   | 12152.4 | 1853.3 |

| I2TRIM0   | 12290.7 | 1853.3 |

| I2TRIM1   | 12431.6 | 1853.3 |

| I2TRIM2   | 12572.5 | 1853.3 |

| 12_TEST   | 12783.7 | 1853.3 |

| VTRIM0    | 13018.8 | 1853.3 |

| VTRIM1    | 13159.7 | 1853.3 |

| VTRIM2    | 13300.6 | 1853.3 |

| VTRIM3    | 13441.5 | 1853.3 |

| DRTKN     | 13885.6 | 1853.3 |

| GNDA      | 14101.4 | 1853.3 |

| VCC       | 14294.1 | 1853.3 |

| ASTER_OUT | 14556.2 | 1853.3 |

| RTKNB     | 14976.2 | 1853.3 |

| GNDA      | 15261   | 1853.3 |

| ESTC      | 15538.3 | 1853.3 |

Notes:

#### **CLARE LOCATIONS**

Clare Headquarters 78 Cherry Hill Drive Beverly, MA 01915 Tel: 1-978-524-6700 Fax: 1-978-524-4900 Toll Free: 1-800-27-CLARE

Clare Micronix Division 145 Columbia Aliso Viejo, CA 92656-1490 Tel: 1-949-831-4622 Fax: 1-949-831-4628

### **SALES OFFICES**

#### **AMERICAS**

## **Americas Headquarters**

Clare 78 Cherry Hill Drive Beverly, MA 01915 Tel: 1-978-524-6700 Fax: 1-978-524-4900 Toll Free: 1-800-27-CLARE

#### **Eastern Region**

Clare 603 Apache Court Mahwah, NJ 07430 Tel: 1-201-236-0101 Fax: 1-201-236-8685 Toll Free: 1-800-27-CLARE

#### **Central Region**

Clare Canada Ltd. 3425 Harvester Road, Suite 202 Burlington, Ontario L7N 3N1 Tel: 1-905-333-9066 Fax: 1-905-333-1824

#### Western Region

Clare 1852 West 11th Street, #348 Tracy, CA 95376 Tel: 1-209-832-4367 Fax: 1-209-832-4732 Toll Free: 1-800-27-CLARE

#### Canada

Clare Canada Ltd. 3425 Harvester Road, Suite 202 Burlington, Ontario L7N 3N1 Tel: 1-905-333-9066 Fax: 1-905-333-1824

#### **EUROPE**

#### European Headquarters

CP Clare nv Bampslaan 17 B-3500 Hasselt (Belgium) Tel: 32-11-300868 Fax: 32-11-300890

#### France

Clare France Sales Lead Rep 99 route de Versailles 91160 Champlan France Tel: 33 1 69 79 93 50 Fax: 33 1 69 79 93 59

#### Germany

Clare Germany Sales ActiveComp Electronic GmbH Mitterstrasse 12 85077 Manching Germany Tel: 49 8459 3214 10 Fax: 49 8459 3214 29

#### Italy

C.L.A.R.E.s.a.s. Via C. Colombo 10/A I-20066 Melzo (Milano) Tel: 39-02-95737160 Fax: 39-02-95738829

#### Sweden

Clare Sales Comptronic AB Box 167 S-16329 Spånga Tel: 46-862-10370 Fax: 46-862-10371

#### **United Kingdom**

Clare UK Sales Marco Polo House Cook Way Bindon Road Taunton UK-Somerset TA2 6BG Tel: 44-1-823 352541 Fax: 44-1-823 352797

#### ASIA PACIFIC

#### Asian Headquarters

Clare Room N1016, Chia-Hsin, Bldg II, 10F, No. 96, Sec. 2 Chung Shan North Road Taipei, Taiwan R.O.C. Tel: 886-2-2523-6368 Fax: 886-2-2523-6369

#### http://www.clare.com

Clare cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in this Clare product. No circuit patent licenses nor indemnity are expressed or implied. Clare reserves the right to change the specification and circuitry, without notice at any time. The products described in this document are not intended for use in medical implantation or other direct life support applications where malfunction may result in direct physical harm, injury or death to a person.

Specification: DS-MXED102-R2 ©Copyright 2001, Clare, Inc. All rights reserved. Printed in USA. 5/21/01